#### **Digital Computers**

Introduction, Block diagram of Digital Computer, Definition of Computer Organization, Computer Design and Computer Architecture.

#### **Register Transfer Language and Micro operations**

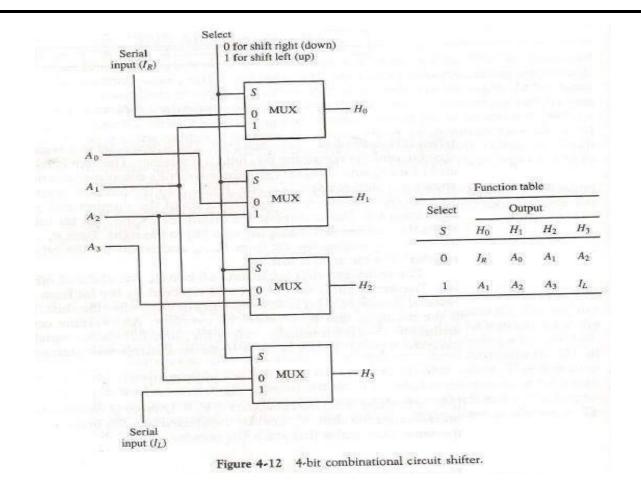

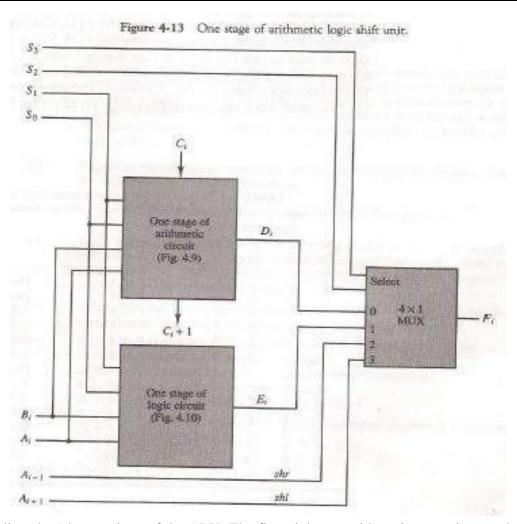

Register Transfer language, Register Transfer, Bus and memory transfers, Arithmetic Micro operations, logic micro operations, shift micro operations, Arithmetic logic shift unit.

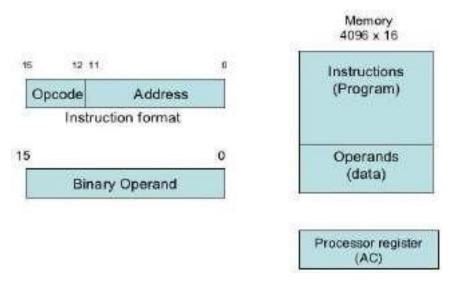

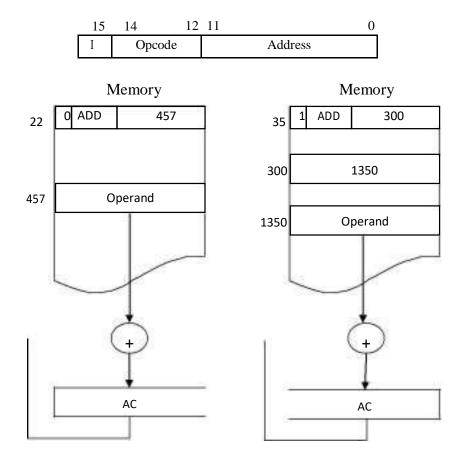

#### **Basic Computer Organization and Design**

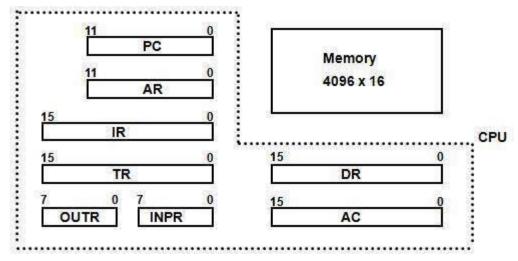

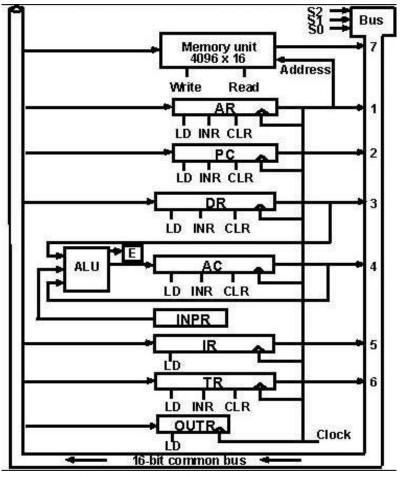

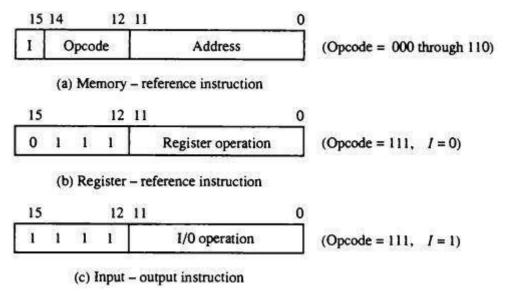

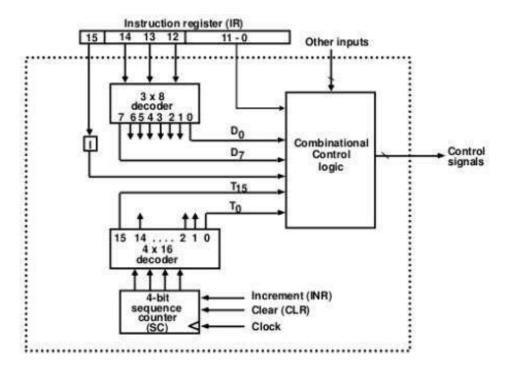

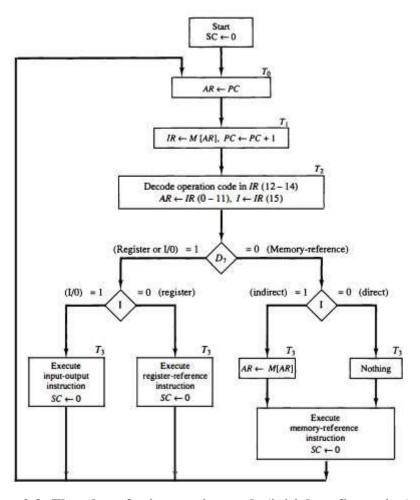

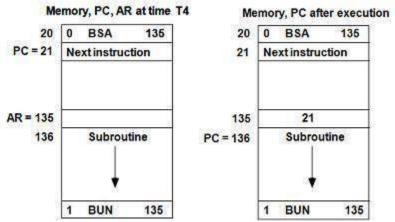

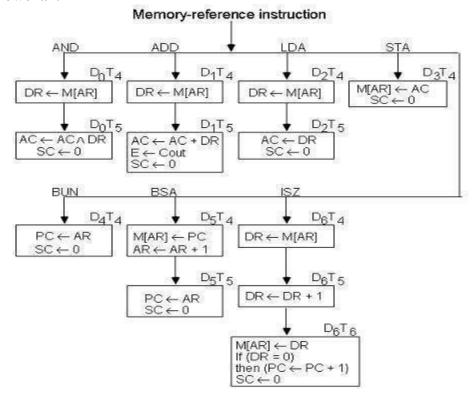

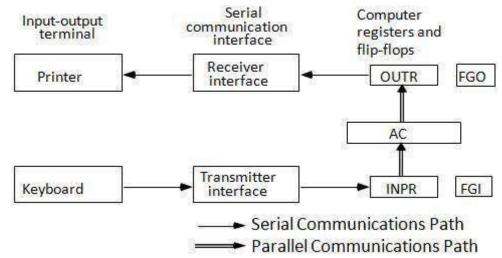

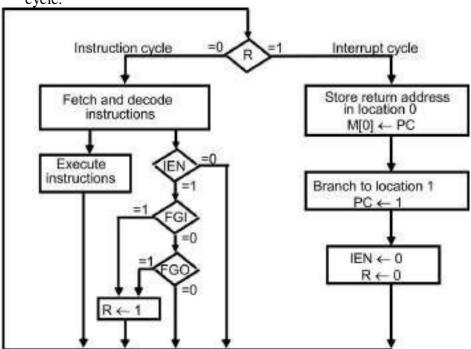

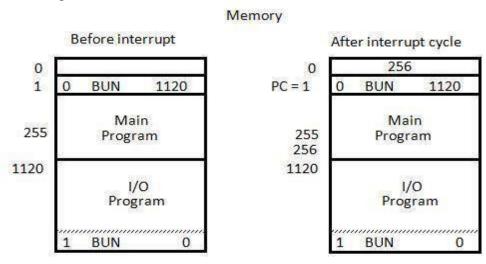

Instruction codes, Computer Registers Computer instructions, Timing and Control, Instruction cycle, Memory Reference Instructions, Input – Output and Interrupt.

## OMPUTER URGANIZATION AND

### ARCHITECTURE

# UNIT-I - Part I

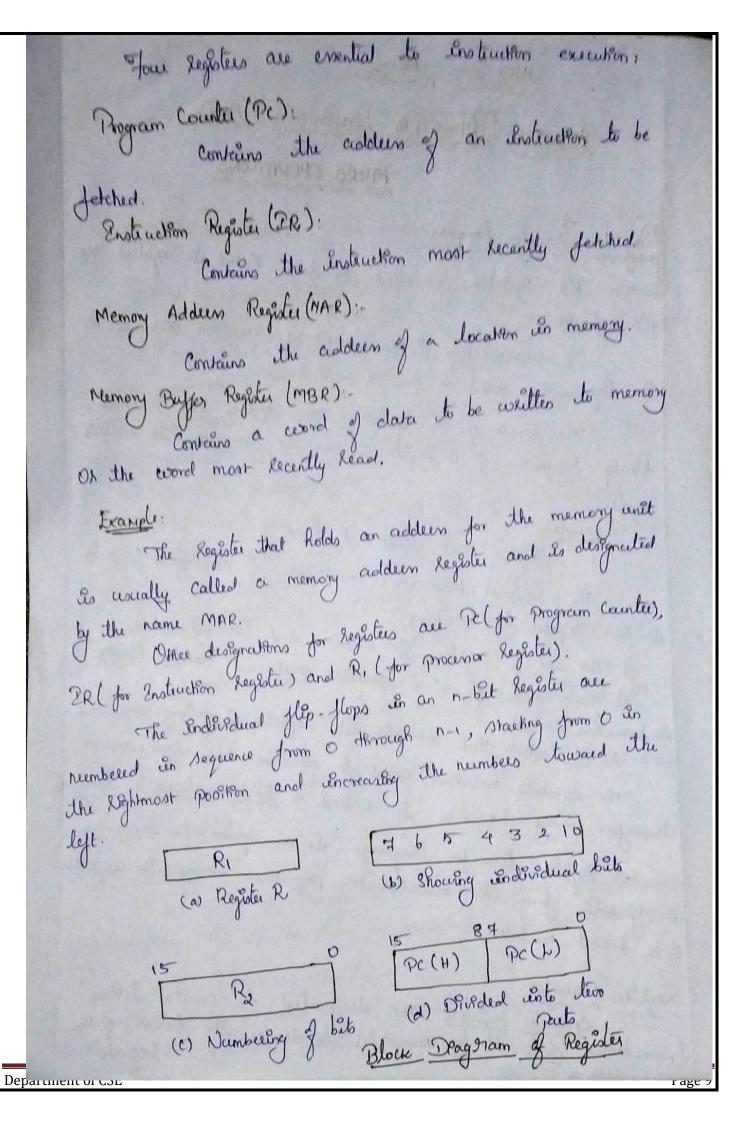

DIGITAL COMPUTERS The digital computer is a digital system that performs vactous Computational lasks. Digital Computers une the benaly number systems Introduction: which has two digits: O and i, of bloomy digit is called a bit. A Computer system & Sometimes Subdirected ento luo Jeurctional entities: The Raedwale of the computer consists of all the electronic 3) Kaldwale Components and electromechanical devices that complise the Physical Computer software cornests of the Enstructions and data that the Computer manipulates to perform various data-processing tasks.

A sequence of instructions for the computer so called a program. The data that are manipulated by the program constitute the

The hardware of the computer is usually divided into data base.

there major processing unit [coo) Contains an aeithmetic and

The Central Mocerning data, a number of Segistees for shoring

legic unit for manipulating there major parts. data and control chaits for fetching and executing instructions, and data. It is called a handom-access memory. [RAM]

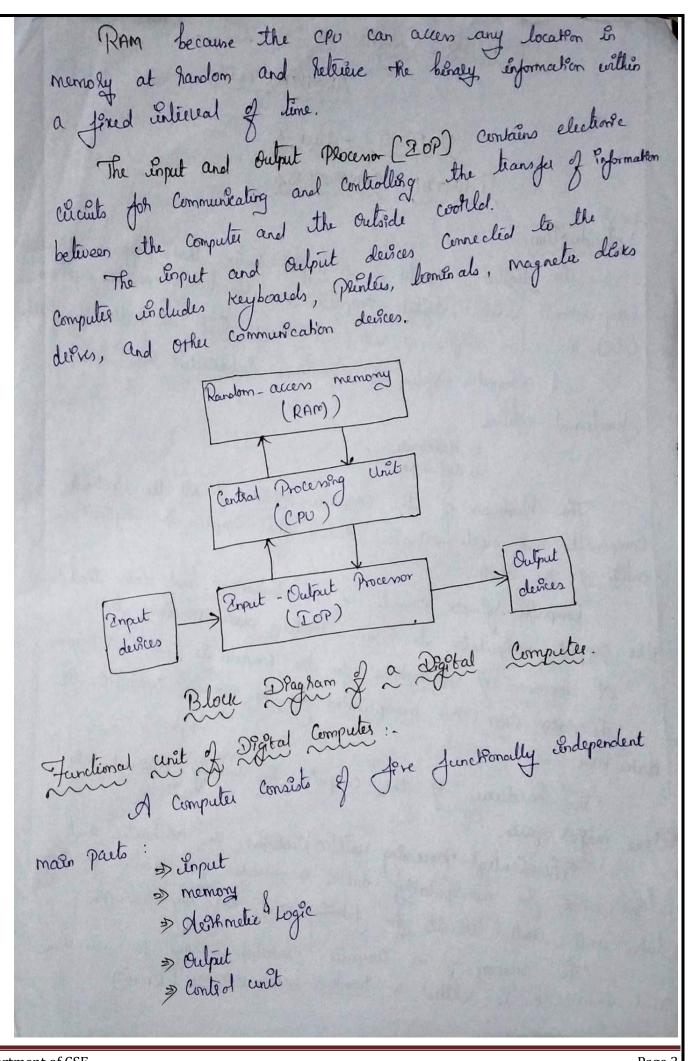

The Enput unit accepts coded Enformation from Ruman Operator from an electromechanical deine such as keyboard on 3 from other computers over digital communication lines The Enformation esther stored in computers memory for Juliue Reference or Eromedialety used by ALU to perform The processing steps are determined by a program stoked desiled Operation. Finally, the results are sent back to the outside coords in memory All of these Operations are coordinated by the Control through the Output went. Anknuke cenet. Memory, Control Output Processor Basic Jurchonal with of a Computer Computer Organization is concerned with the way Computer Organization! the Raedwale Components Operate and the way they are Connected together to form the computer systems. The warrows components are assumed to be in place and the task is to Envestigate the Organization structure to verify that the Computer parts operate as centended. Computer Organization Refers to the Operational units and their interconnections that healize the architectural specy?calons.

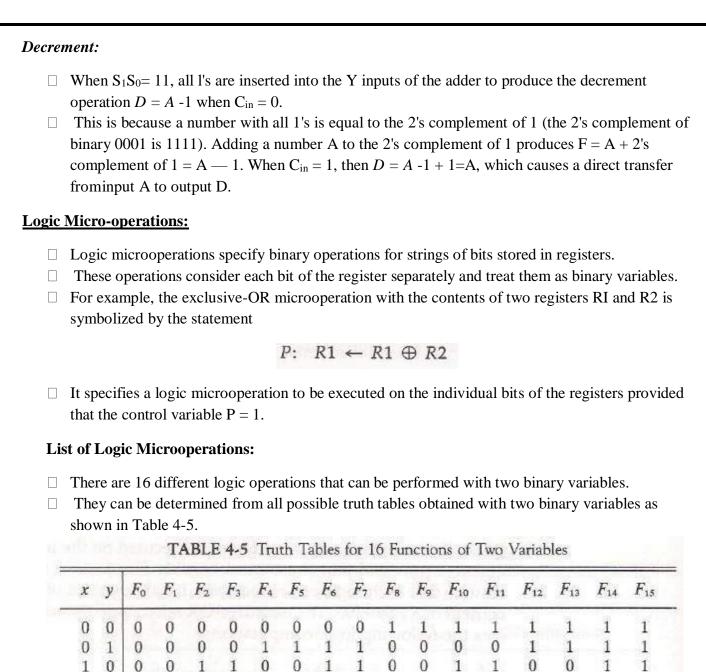

Organi Zatronal attributes Include those hardware Example: details transparent to the programmer, such as control memory untufaces between the computer and perpherals, and the memory - Design of the Components and Jeunethonal blocks using which technology used. Computer systems are built. Computer Design is concerned with the hardware design of the computer. Once the computer specifications are formulated, Et is the task of the designer to develop hardware for the System. It is conceined with the determination of what haedware should be used and how the parts should be Connected.

This aspect of computer hardware as sometimes referred le as computer implementation. Computer d'relatecture às concerned with the structure and Computer Architecture: behavior of the computer as seen by the uses. Et includes the Enformation formats, the Enstruction set and techniques for addensing Memory. The architectural design of a computer system is concerned cert the specifications of the various functional modules, such as processors and memories and structuring them together wints a Computer Architecture: lejees to those attibules of a system Computer system. Uissible to a programe or, put another way, those attibutes That have a direct impact on the logical execution of a program.

Architectural attibutes include the instructions set, The B Example number of bits used to Represent VaiPour data lyres (og numbers, characters), 210 mechanisms and techniques for addressing memory. Two base types of computer architecture are you new mount auchibelieu and Haward archibelieu. En a Von-neumann auchibeture, the same memory and Von - Neumann Architecture: bus are concreted used to stoke both data and instructions Elice Et cannot access program memory and data memory Strutraneously, the Von-neumann architecture as surceptible to that hen the program. battlenecks and system preformance is offected. The structure of a computer system as being composed 7) The central authorates cent, which today is called the authorate of the flouring components. logic unit (Abo). This writ performs the computers computational 2). Nemory, Nou specifically, the computer's main, or fast, and logical Junctions. memory such as handom accen memory (RAM); 3) of central unit that directs Other components of the computer to Perform certain actions, such as directing the fitching of data or instruction from memory to be the processed by the sky and 4) man-machine untispaces; (in) input and output deixes, Such as keyboard for Enput and desplay monitor for output. The Harvard architecture stokes machine instructions and Harvard Architecture. data in reparate memory units that are connected by deferent

Proces to corre with, so there is a memory legister for machine renotements and another memory legister for data. Computers designed with the Husbard authorities are able to hun a program and cover dotta independently and therefore to hun a program and accent dotta independently and therefore to hun a program and accent dotta independently and therefore to hun a program and accent dotta independently and therefore to hundred architecture has a start repaidtion between data.

Harvard architecture has a start repaidtion between data and cook. Thus, Harvard architecture is more complicated but and cook. Thus, Harvard architecture is more complicated but separate pipelines remove the bottleneck.

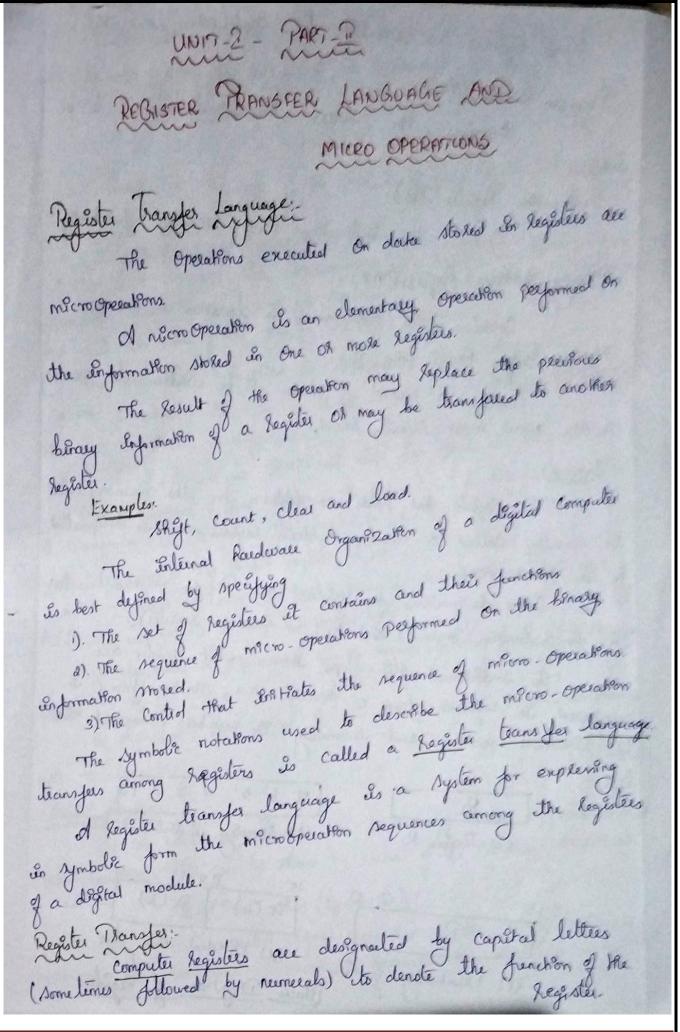

Information transfer from one register to another is designed un symbolic form by means of a replacement operators. The Statement (K) ← R, denotes a transfer of the content of register R, Esto legistes Block diagram explanation: In block diagram, the leplesentation of legisters in block diagram form. The most common way to replesent a register to by a rectangular box with the name of the register inside of diagram (a). • The Individual buts can be distinguished as in diagram (b). • The numberry of bits in a 16-bit legiter can be marked on stop of the box as shown in dragram (c). · A 16-bût legister is Packitioned unto two poets in diagram (d). · But thritiugh of are assigned the symbol L (for low byte) and but 8 through is are assigned the symbol H (for high byte). · The name of the 16-but legister is PC. • The Hymbol PC (0-7) or PC(L) Refers to the low-order byte and PC(8-15) or PC(H) to the Righ-order byte. De designates a replacement of the content of R, by the By definition, the content of the source Register R. does not change Content of R1 after the transfer. Cinted Junchon: If we want the transfer to occur only under a pledetermined Control Condition. This can be shown by means of an ey then 21 (P=1) then (R - R1). Where P is a control signal generated in the control Materners

section. It is sometimes convenient to departe the control chairables

Department of CSL

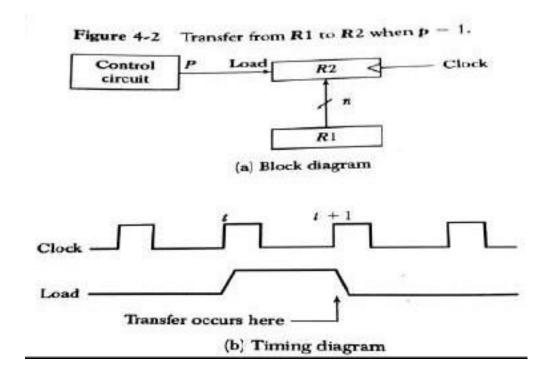

· By Register Ro has a load input that is achivated by the control

Ser is a numed that the control variable is grachionized with the same clock as the one applied to the segister.

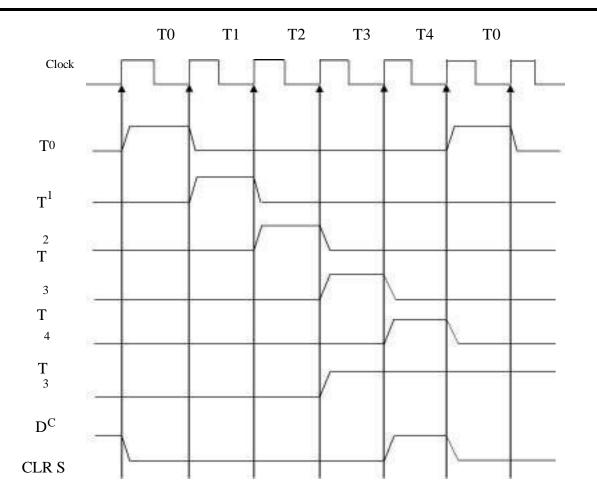

Timing Deagram Explanation!

· P is activated in the control section by the living edge of

a clock Pulse at time t.

The next possitive transition of the clock pulse at time tot.

Indo the load angut active and the data inputs of R2 are then

loaded into the legister in possible.

P may go back to 0 cet time t+1. Otherwise, the transfer will occur with every clock Pulse transition cohile P Remains active.

· Note that the clock is not included as a Carpable is the

Register transfer statements. 8 & is assumed that all transfers occur during a clock edge

Even though the control condition such as P becomes active gust after the t, the actual transfer does not occur until the Register is triggeled by the next possible transition of the clock at time tt.

|                        | with classifica                                                |                      |

|------------------------|----------------------------------------------------------------|----------------------|

| Symbol                 | Description                                                    | Examples             |

| Letters (and numerals) | Denotes a legister                                             | MAR, R2              |

| Parentherest)          | Denotes a part of a Register                                   | Rg(0-7), Rg(L)       |

| Allow &                |                                                                | R, <- P,             |

| Comma,                 | Denotes transfer of Enformation Separates two inference ations | $R_2 \leftarrow R_1$ |

|                        | Park and otherwise Latin                                       | $R_1 \leftarrow R_2$ |

|                        |                                                                |                      |

Table Explanation:

The basic symbols of the Register transfer notation are listed in above table.

Department of CSE

· Registes are denoted by applial letters and neemerals may follow the letters. · Parentheses are used to denote a part of a Register by sperifying the Range of bits 08 by giving a Symbol name to a Pollim of a legister. · The arrow denotes a transfer of information and the direction of Transfer. · A Comma is used to reparate two or more operations that are executed at the same time. • The Hatement T: R, ← R, , R, ← R, elenates an operation that exchanges the Contents of two Registers during one common clock pulse provided that T=1. · This symultaneous operation is possible with registers that Designale Computer proposoftops registées by capital letters. to have edge teiggered flip-flops. The legistes that Rolds an address for the memory unit is denote at Junction. The program counter legister is called Pc. called MAR. 2R Es the Enstruction Register and R. is a processor legister. The Endividual flip-flops in an n-bit Register are numbered cen sequence from 0 to n-1 Bus And Memory Mansfers: Bus langer. Digital computer has many registers and paths must be provided to teansfer information from one legister to another. The number of cires wall be consciented excersive by separate lines are used between each Register and all other registers to the

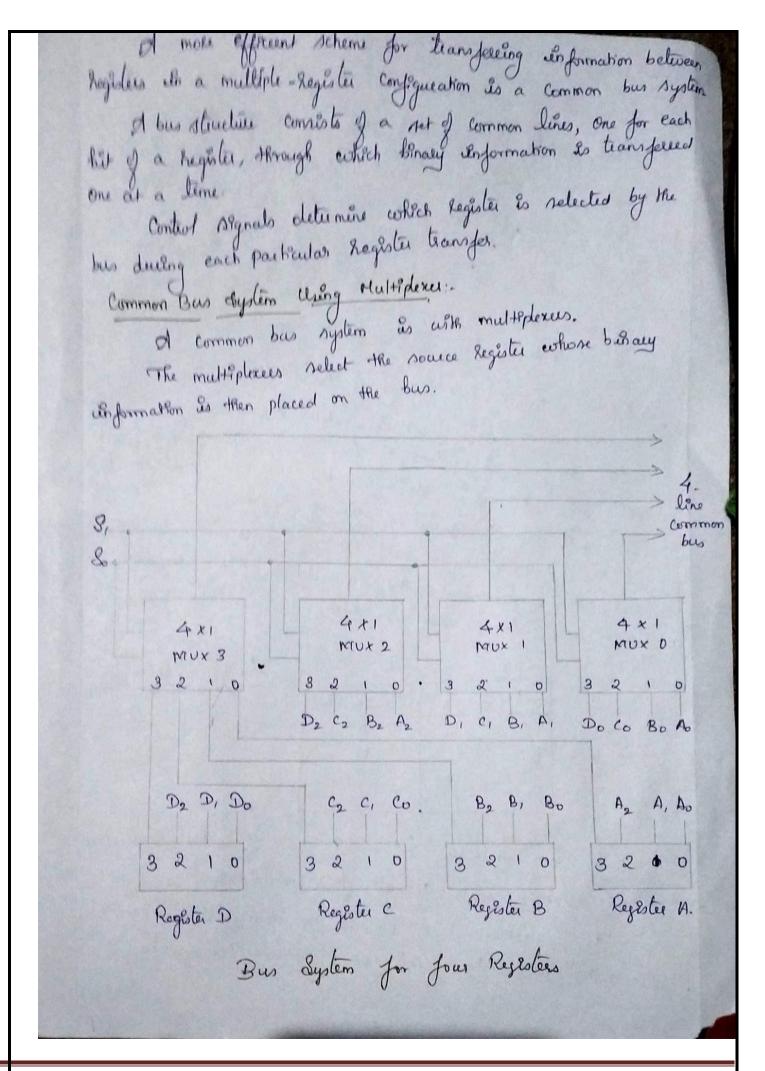

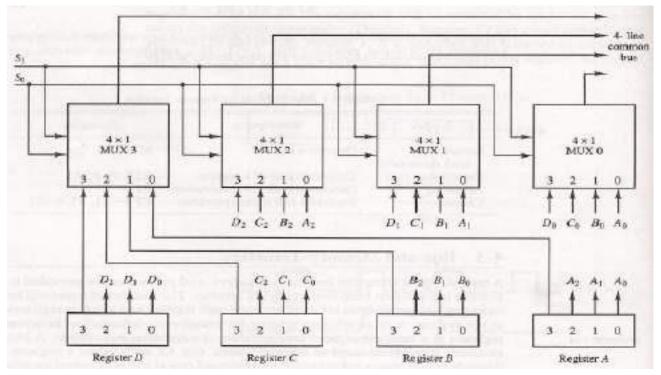

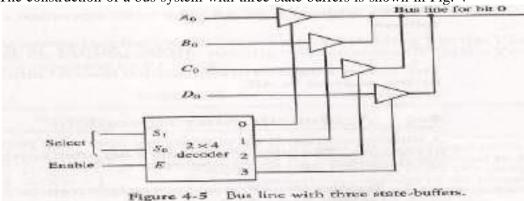

. The Construction of a bus system for four legisters Les Moun in above figuer · Each Register has Jour bits, numbered to through 3. . The bus consists of four 4x1 multiplexus each having four data Espects, o through 3 and two selection inputs 9, En order not to complécate the deagram with 16 lènes Crossing each other, we use labels to show the connections from the outputs of the Registers to the Enputs of the multiplexees Jos example: Gutput 1 & Register A & Connected to Enput 0 of MUXI. because this Input is labeled A,. The dragram shows that the bets in the same styriffcant PONPHON in each Register are connected to the dara inputs of one multiplexes to form one lone of the bus. Thus MUX o multiplexees the four o bets of the Registees, Mux 1 multiplexees the four 1 bits of the registers, and somelarly for the other two bets.

| 3, | So | Register Selecter |

|----|----|-------------------|

| 0  | 0  | Δ                 |

| 0  | 1  | B                 |

| 1  | 0  | c                 |

| 1  | 1  | D                 |

Function Table for bus

The two selection lines 3, and 30 are connected to the selection Enputs of all four multiplexees.

The selection benes choose the four bits of one Register and transfer them ento the four line common bus.

#### **Unit-1: REGISTER TRANSFER AND MICROOPERATIONS**

| CONTENTS: |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|           | Register Transfer Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|           | Register Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|           | Bus And Memory Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|           | Types of Micro-operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|           | Arithmetic Micro-operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|           | Logic Micro-operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|           | Shift Micro-operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|           | Arithmetic Logic Shift Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| BASIC     | C DEFINITIONS:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|           | A digital system is an interconnection of digital hardware modules.  The modules are registers, decoders, arithmetic elements, and control logic.  The various modules are interconnected with common data and control paths to form a digital computer system.  Digital modules are best defined by the registers they contain and the operations that are performed on the data stored in them.  The operations executed on data stored in registers are called <i>microoperations</i> .  A <i>microoperation</i> is an elementary operation performed on the information stored in one or more registers.  The result of the operation may replace the previous binary information of a register or may be transferred to another register.  Examples of microoperations are shift, count, clear, and load.  The internal hardware organization of a digital computer is best defined by specifying: |  |  |  |

|           | 1. The set of registers it contains and their function.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|           | <ul><li>2. The sequence of microoperations performed on the binary information stored in the registers.</li><li>3. The control that initiates the sequence of microoperations.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| REGI      | STER TRANSFER LANGUAGE:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|           | The symbolic notation used to describe the micro-operation transfer among registers is called RTL (Register Transfer Language).  The use of <i>symbols</i> instead of a <i>narrative explanation</i> provides an organized and concise manner for listing the micro-operation sequences in registers and the control functions that initiate them.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|        | A register transfer language is a system for exp                                                    |                                                         |  |  |

|--------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------|--|--|

|        | sequences among the registers of a digital modulities a convenient tool for describing the internal | le. I organization of digital computers in concise and  |  |  |

|        | precise manner.                                                                                     | if organization of digital computers in concise and     |  |  |

| Regist | ters:                                                                                               |                                                         |  |  |

|        | Computer registers are designated by upper cas                                                      | e letters (and optionally followed by digits or         |  |  |

|        | letters) to denote the function of the register.                                                    |                                                         |  |  |

|        | For example, the register that holds an address                                                     |                                                         |  |  |

|        | address register and is designated by the name l                                                    |                                                         |  |  |

|        | (for processor register).                                                                           | gram counter), $IR$ (for instruction register, and $R1$ |  |  |

|        |                                                                                                     | numbered in sequence from 0 through n-1, starting       |  |  |

|        | from 0 in the rightmost position and increasing                                                     |                                                         |  |  |

|        | Figure 4-1 shows the representation of registers                                                    | in block diagram form.                                  |  |  |

|        | Figure 4-1 Bloo                                                                                     | 1. 1:                                                   |  |  |

|        | rigure 4-1 Bloc                                                                                     | k diagram of register.                                  |  |  |

|        | R1                                                                                                  | 7 6 5 4 3 2 1 0                                         |  |  |

|        | (a) Register R                                                                                      | (b) Showing individual bits                             |  |  |

|        |                                                                                                     |                                                         |  |  |

|        | 15 0                                                                                                | 15 8 7 0                                                |  |  |

|        | R2                                                                                                  | PC (H) PC (L)                                           |  |  |

|        |                                                                                                     |                                                         |  |  |

|        | (c) Numbering of bits                                                                               | (d) Divided into two parts                              |  |  |

|        | The most common way to represent a register in register in Fig. 4.1(a)                              | s by a rectangular box with the name of the             |  |  |

|        | register inside, as in Fig. 4-1(a).<br>The individual bits can be distinguished as in (b            | ))                                                      |  |  |

|        |                                                                                                     |                                                         |  |  |

|        | _                                                                                                   | ). Bits 0 through 7 are assigned the symbol L (for      |  |  |

|        | low byte) and bits 8 through 15 are assigned the                                                    |                                                         |  |  |

|        | The name of the 16-bit register is <i>PC</i> . The sym                                              |                                                         |  |  |

|        | byteand PC (8-15) or $PC(H)$ to the high-order                                                      | byte.                                                   |  |  |

| Regist | ter Transfer:                                                                                       |                                                         |  |  |

|        | Information transfer from one register to anothe replacement operator.                              | er is designated in symbolic form by means of a         |  |  |

|        | The statement $\mathbf{R2} \leftarrow \mathbf{R1}$ denotes a transfer of th                         | e content of register R1 into register R2.              |  |  |

|        | It designates a replacement of the content of R2                                                    |                                                         |  |  |

|        | By definition, the content of the source register                                                   | -                                                       |  |  |

|        | If we want the transfer to occur only under a pr                                                    | edetermined control condition then it can be            |  |  |

|        | shown by an if-then statement.                                                                      |                                                         |  |  |

|        | if (P=1) then <b>R2← R1</b>                                                                         |                                                         |  |  |

t+1.

☐ The basic symbols of the register transfer notation are listed in below table

| Symbol                | Description                     | Examples         |

|-----------------------|---------------------------------|------------------|

| Letters(and numerals) | Denotes a register              | MAR, R2          |

| Parentheses ( )       | Denotes a part of a register    | R2(0-7), R2(L)   |

| Arrow <               | Denotes transfer of information | R2 < R1          |

| Comma ,               | Separates two microoperations   | R2 < R1, R1 < R2 |

| Ш | A comma is used to separat              | e two or more operations that are executed at the same time.        |

|---|-----------------------------------------|---------------------------------------------------------------------|

|   | The statement                           |                                                                     |

|   | $T: R2 \leftarrow R1, R1 \leftarrow R2$ | (exchange operation)                                                |

|   | denotes an operation that ex            | schanges the contents of two rgisters during one common clock pulse |

|   | provided that T=1.                      |                                                                     |

#### **Bus and Memory Transfers:**

| A more efficient scheme for transferring information between registers in a multiple-register   |  |  |

|-------------------------------------------------------------------------------------------------|--|--|

| configuration is a Common Bus System.                                                           |  |  |

| A common bus consists of a set of common lines, one for each bit of a register.                 |  |  |

| Control signals determine which register is selected by the bus during each particular register |  |  |

| transfer.                                                                                       |  |  |

| Different ways of constructing a Common Bus System                                              |  |  |

| ✓ Using Multiplexers                                                                            |  |  |

| ✓ Using Tri-state Buffers                                                                       |  |  |

#### **Common bus system is with multiplexers:**

| Ш | The multiplexers select the source register whose binary information is then placed |

|---|-------------------------------------------------------------------------------------|

|   | on the bus.                                                                         |

|   | The construction of a bus system for four registers is shown in below Figure.       |

- $\square$  The bus consists of four 4 x 1 multiplexers each having four data inputs, 0 through 3, and two selection inputs,  $S_1$  and  $S_0$ .

- $\square$  For example, output 1 of register A is connected to input 0 of MUX 1 because this input is labelled  $A_1$ .

- ☐ The diagram shows that the bits in the same significant position in each register are connected to the data inputs of one multiplexer to form one line of the bus.

- ☐ Thus MUX 0 multiplexes the four 0 bits of the registers, MUX 1 multiplexes the four 1 bits of theregisters, and similarly for the other two bits.

- ☐ The two selection lines Si and So are connected to the selection inputs of all four multiplexers.

- ☐ The selection lines choose the four bits of one register and transfer them into the four-line common bus.

- When  $S_1S_0 = 00$ , the 0 data inputs of all four multiplexers are selected and applied to the outputs that form the bus.

- ☐ This causes the bus lines to receive the content of register A since the outputs of this register are connected to the 0 data inputs of the multiplexers.

- $\Box$  Similarly, register *B* is selected if  $S_1S_0 = 01$ , and so on.

- ☐ Table 4-2 shows the register that is selected by the bus for each of the four possible binary value of the selection lines.

| $S_1$ | $S_0$ | Register selected |

|-------|-------|-------------------|

| 0     | 0     | A                 |

| 0     | 1     | В                 |

| 1     | 0     | С                 |

| 1     | 1     | D                 |

☐ In general a bus system has

✓ multiplex "k" Registers

- ✓ each register of "n" bits

- ✓ to produce "n-line bus"

- $\checkmark$  no. of multiplexers required = n

- ✓ size of each multiplexer =  $k \times 1$

- ☐ When the bus is includes in the statement, the register transfer is symbolized as follows:

#### $BUS \leftarrow C, R1 \leftarrow BUS$

☐ The content of register C is placed on the bus, and the content of the bus is loaded into register R1 by activating its load control input. If the bus is known to exist in the system, it may be convenient just to show the direct transfer.

#### **R1← C**

#### **Three-State Bus Buffers:**

- ☐ A bus system can be constructed with three-state gates instead of multiplexers.

- ☐ A three-state gate is a digital circuit that exhibits three states.

- ☐ Two of the states are signals equivalent to logic 1 and 0 as in a conventional gate.

- $\Box$  The third state is a *high-impedance state*.

- ☐ The high-impedance state behaves like an open circuit, which means that the output is disconnected and does not have logic significance.

- Because of this feature, a large number of three-state gate outputs can be connected with wires to form a common bus line without endangering loading effects.

- ☐ The graphic symbol of a three-state buffer gate is shown in Fig. 4-4.

Figure 4-4 Graphic symbols for three-state buffer.

- ☐ It is distinguished from a normal buffer by having both a normal input and a control input.

- ☐ The control input determines the output state. When the control input is equal to 1, the output is enabled and the gate behaves like any conventional buffer, with the output equal to the normal input.

- □ When the control input is 0, the output is disabled and the gate goes to a high-impedance state, regardless of the value in the normal input.

☐ The construction of a bus system with three-state buffers is shown in Fig. 4

|       | The outputs of four buffers are connected together to form a single bus line.  The control inputs to the buffers determine which of the four normal inputs will communicate with the bus line.                                                  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | No more than one buffer may be in the active state at any given time. The connected buffers must be controlled so that only one three-state buffer has access to the bus line while all other buffers are maintained in a high impedance state. |

|       | One way to ensure that no more than one control input is active at any given time is to use a                                                                                                                                                   |

|       | decoder, as shown in the diagram.  When the enable input of the decoder is 0, all of its four outputs are 0, and the bus line is in a                                                                                                           |

|       | high-impedance state because all four buffers are disabled.                                                                                                                                                                                     |

|       | When the enable input is active, one of the three-state buffers will be active, depending on the binary value in the select inputs of the decoder.                                                                                              |

| Mem   | ory Transfer:                                                                                                                                                                                                                                   |

|       | The transfer of information from a memory word to the outside environment is called a <i>read</i> operation.                                                                                                                                    |

|       | The transfer of new information to be stored into the memory is called a <i>write</i> operation.                                                                                                                                                |

|       | A memory word will be symbolized by the letter M.  The particular memory word among the many available is selected by the memory address during                                                                                                 |

|       | The particular memory word among the many available is selected by the memory address during the transfer.                                                                                                                                      |

|       | It is necessary to specify the address of M when writing memory transfer operations.  This will be done by enclosing the address in square brackets following the letter M.                                                                     |

|       | Consider a memory unit that receives the address from a register, called the address register,                                                                                                                                                  |

|       | symbolized by AR.  The data are transferred to another register, called the data register, symbolized by DR.                                                                                                                                    |

|       | The read operation can be stated as follows:                                                                                                                                                                                                    |

|       | Read: DR<- M [AR]                                                                                                                                                                                                                               |

|       | This causes a transfer of information into DR from the memory word M selected by the address in AR.                                                                                                                                             |

|       | The write operation transfers the content of a data register to a memory word M selected by the address. Assume that the input data are in register R1 and the address is in AR.                                                                |

|       | The write operation can be stated as follows:                                                                                                                                                                                                   |

|       | Write: M [AR] <- R1                                                                                                                                                                                                                             |

| Types | of Micro-operations:                                                                                                                                                                                                                            |

|       | <u>Register Transfer Micro-operations:</u> Transfer binary information from one register to another.                                                                                                                                            |

|       | Arithmetic Micro-operations: Perform arithmetic operation on numeric data stored in registers.                                                                                                                                                  |

|       | <u>Logical Micro-operations:</u> Perform bit manipulation operations on data stored in registers.<br><u>Shift Micro-operations:</u> Perform shift operations on data stored in registers.                                                       |

|       | Register Transfer Micro-operation doesn't change the information content when the binary information moves from source register to destination register.                                                                                        |

|       |                                                                                                                                                                                                                                                 |

|              | Other three types of micro-operations change the information change the information content during the transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>Arith</u> | metic Micro-operations:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|              | The basic arithmetic micro-operations are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|              | <ul> <li>Addition</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              | o Subtraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

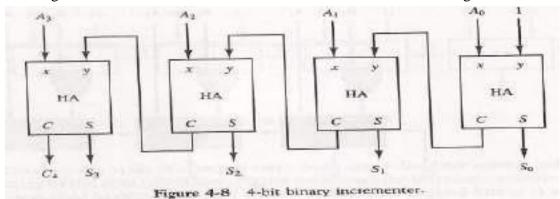

|              | o Increment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|              | o Decrement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| П            | O Shift  The arithmetic Micro operation defined by the statement below specifies the odd micro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|              | The arithmetic Micro-operation defined by the statement below specifies the add micro-operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|              | $R3 \leftarrow R1 + R2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|              | It states that the contents of R1 are added to contents of R2 and sum is transferred to R3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|              | To implement this statement hardware requires 3 registers and digital component that performs addition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

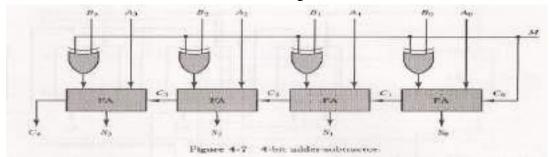

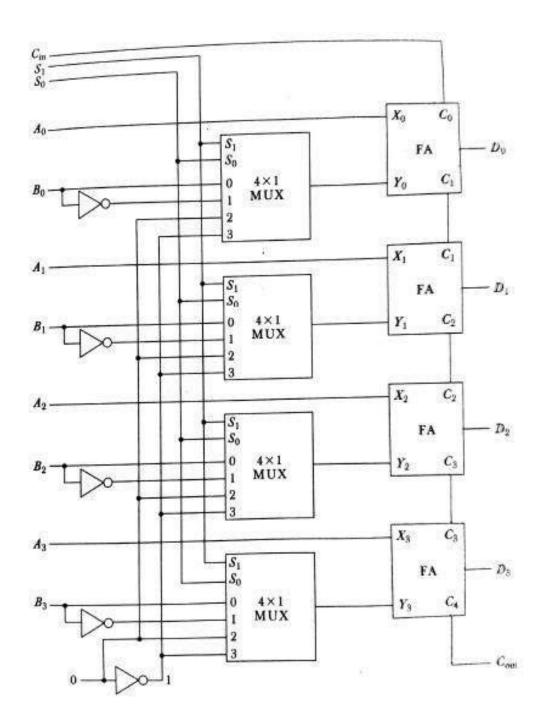

|              | Subtraction is most often implemented through complementation and addition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|              | The subtract operation is specified by the following statement $R3 \leftarrow R1 + R2 + 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |